The Design for Testability (DFT)

The Design for Testability (DFT) course begins with semiconductor manufacturing fundamentals and core fault modelling, covering essential concepts like stuck-at, transition, and delay faults. Students progress through scan design and flip-flop architecture, learning the practical RTL-to-netlist insertion flow and ATPG pattern generation.

The curriculum then tackles advanced industry topics such as scan compression, JTAG boundary scan, and memory testing using specific MBIST algorithms like March C. Finally, the program addresses complex SoC challenges, including power-aware DFT, automotive functional safety under ISO 26262, and real-world debug techniques for broken scan chains.

Design For Testability

Module 1 | Semiconductor Test Fundamentals

-

Why testing is mandatory in semiconductor manufacturing

-

Manufacturing Defects vs. Design Bugs

-

Test Economics: Cost of Test and Yield Impact

-

Manufacturing Flow: Fab → Wafer Test → Packaging → Final Test

-

Role of DFT Engineer in the Industry

Tool Coverage Options

Zerlon is a leading VLSI training institute offering job-oriented semiconductor courses designed to bridge the gap between academic learning and real industry requirements. With over 9 years of experience in VLSI education.

Synopsys (DFTMAX / TetraMAX)

Cadence (Modus)

Siemens EDA (Tessent)

Pay Using Your Preferred Method

UPI

Credit/Debit card

Net banking

Wallet

On Industry-based VLSI Courses at Zerlon Semi at an amazing 30% Offer and Get Your Dream Job!

Specialized VLSI Learning Paths

Hands-On ASIC and SoC Exposure

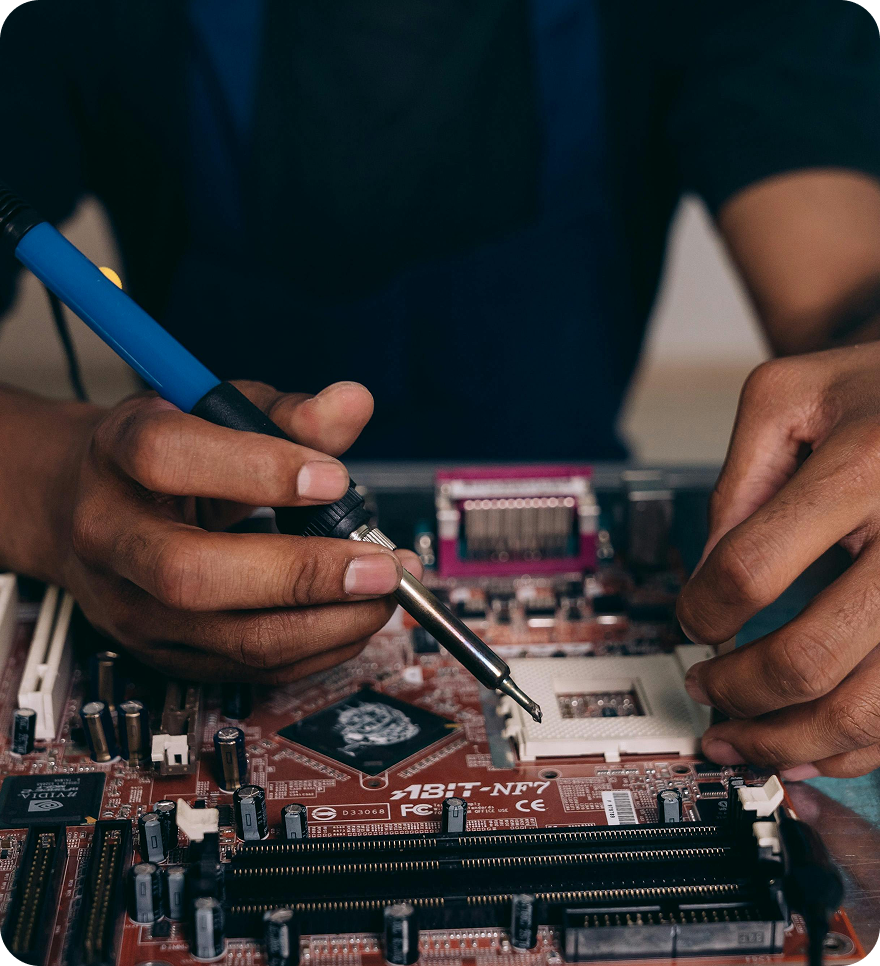

Tool-Based Practical Training

Placement-Oriented Skill Development

Mentorship from Industry Professionals

Tool-Based Practical Training

Structured Interview Preparation Support

Scholarship Details

GATE scores

Candidates with valid GATE scores are eligible for an additional scholarship benefit.

Scholarship Process

Complete the online application and technical interview to begin the scholarship process.

60% in the online assessment

Score more than 60% in the online assessment to move forward in the scholarship process.

Zerlon Oriented Scholarship Scheme Curation

Academic Eligibility

Degree, 12th & 10th

Minimum Aggregate

60% and Above

Online Test Score

60% and Above

Scholarship

Up to 5%

Upcoming Batches For Online

Get Hands-On Advanced VLSI Training with 100% Placement Assistance

Training

Start Your Training

Get Hands-On Advanced VLSI Training with 100% Placement Assistance

Training

Start Your Training